3D IC集成和封装概述

引言

随着半导体行业不断追求在更小尺寸中实现更高性能和更多功能,3D集成技术已成为有前途的解决方案。本文概述了关键的3D IC集成和封装技术,包括硅通孔(TSV)、高带宽内存(HBM)以及各种堆叠方法[1]。

3D IC封装

3D IC封装指的是不使用TSV的芯片垂直堆叠。常见的方法有几种:

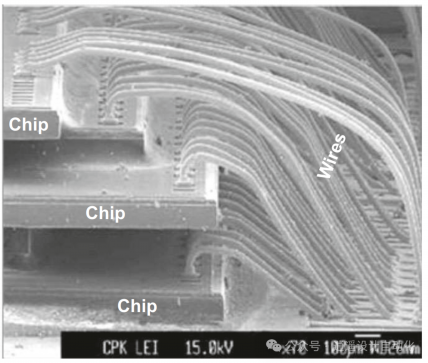

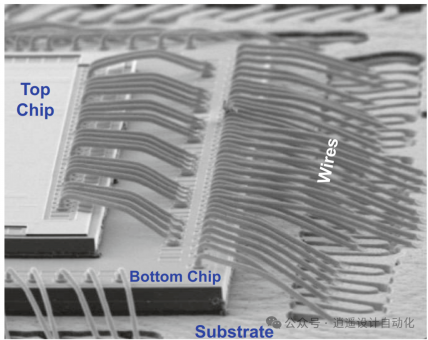

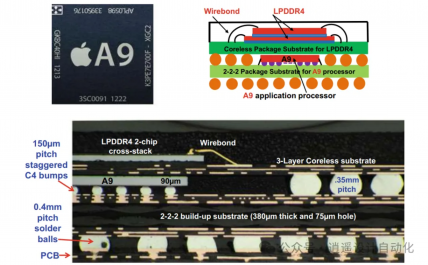

1. 键合:多个芯片堆叠并使用周边的键合线连接。这是成熟的低成本方法,广泛用于内存堆叠(图1和2)。

图1

图2

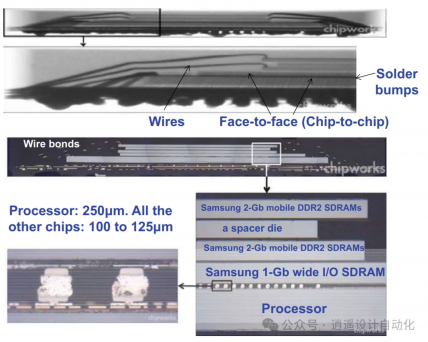

2. 面对面键合: 两个芯片通过微凸点面对面键合,其中一个芯片用键合线连接到基板(图3)。

图3

3. 背对背键合:两个芯片背对背键合,一个芯片倒装到基板上,另一个用键合线连接(图4)。

图4

4. 面对面键合加焊球: 与方法2类似,但使用焊球而不是键合线连接到基板(图5)。

图5

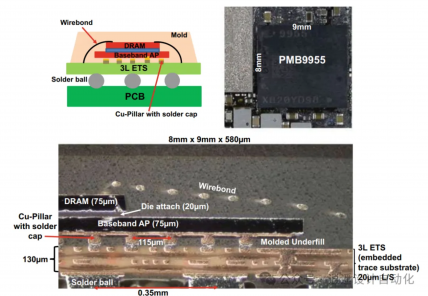

5. 封装叠加封装(PoP): 单独的封装垂直堆叠,通常底部是应用处理器,顶部是内存(图6)。

图6

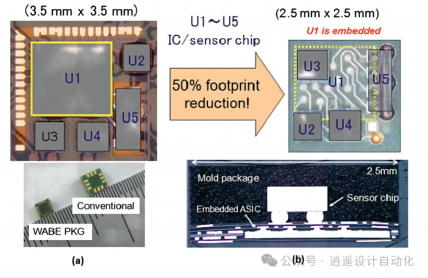

6. 嵌入式芯片: 芯片嵌入到封装基板中(图7)。

图7

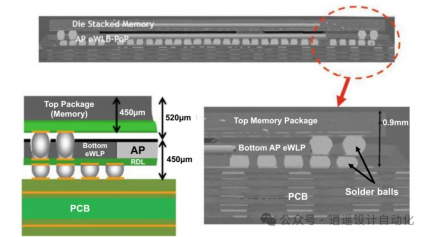

7. 扇出晶圆级封装: 芯片嵌入到模塑化合物中并重新分布,以实现更高的I/O密度(图8)。

图8

每种方法在电气性能、热管理、尺寸和成本方面都有权衡。选择取决于具体的应用需求。

使用TSV的3D IC集成

3D IC集成使用TSV在硅芯片中创建垂直电连接。与传统封装方法相比,可实现更高的互连密度和带宽。关键的3D IC集成技术包括:

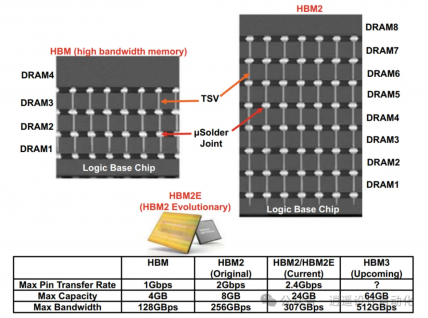

1. 高带宽内存(HBM):HBM使用TSV和微凸点将多个DRAM芯片堆叠在逻辑基础芯片上(图9)。与传统DRAM封装相比,可提供显著更高的内存带宽。HBM对高性能计算、AI和图形应用非常重要。

图9

2. 芯片叠加晶圆(CoW)堆叠: 单个芯片键合到包含TSV的晶圆上的芯片。用于不同类型芯片的异构集成。

3. 晶圆叠加晶圆(WoW)堆叠: 整个晶圆键合在一起,TSV提供垂直连接。可实现很高的互连密度,但需要良好的芯片对芯片对准。

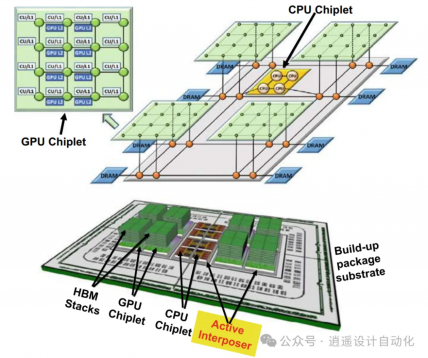

4. 基于中间层的集成: 带有TSV的中间层充当中间基板,连接多个芯片。允许混合不同工艺节点和芯片类型(图10)。

图10

TSV制造和组装

TSV通常使用"中段硅通孔"或"后段硅通孔"工艺制造:

● 中段硅通孔:TSV在前端工艺(FEOL)之后但在后端金属化(BEOL)之前形成。

● 后段硅通孔: TSV在BEOL之后创建,可以从晶圆正面或背面进行。

选择会影响TSV尺寸和制造工艺流程。中段硅通孔更常用于大批量生产。

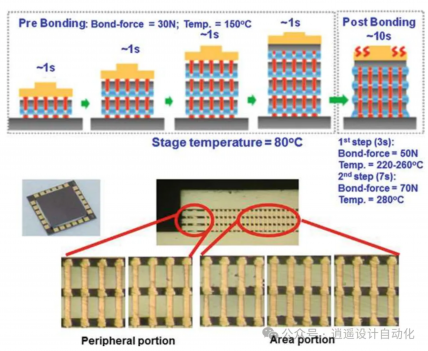

带TSV的3D堆叠组装通常使用热压键合(TCB)和铜柱微凸点。通常使用非导电薄膜(NCF)或浆料(NCP)作为底填以提高可靠性。对于HBM堆叠,芯片逐个键合,可能限制产量。为解决这个问题,已开发出同时键合多个芯片的集体键合方法(图11)。

图11

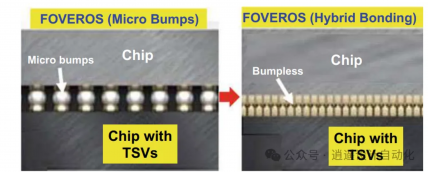

先进的3D集成:混合键合

混合键合是一种先进的互连技术,可以直接键合铜垫而无需焊料凸点。与微凸点方法相比,可实现更细间距的互连。主要优势包括:

● 更高的互连密度

● 改善的电气和热性能

● 减小封装高度

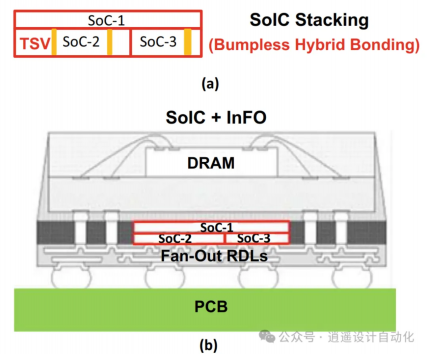

混合键合可用于各种3D集成场景:

1. 带TSV的芯片对芯片: 一个芯片混合键合到另一个含TSV的芯片上(图12和13) 。

图12

图13

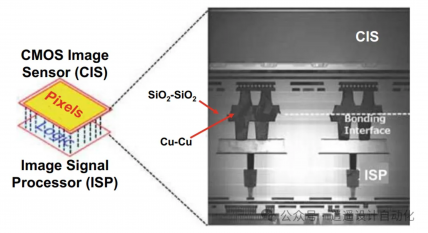

2. 不带TSV的芯片对芯片: 用于不需要TSV的应用, 如堆叠图像传感器(图14)。

图14

3. 芯片对晶圆:单个芯片混合键合到晶圆上的芯片。

4. 晶圆对晶圆: 整个晶圆混合键合在一起。

英特尔、台积电和三星等主要半导体公司正在积极开发用于大批量生产的混合键合能力。

3D IC的设计考虑

3D集成带来了几个独特的设计挑战:

1.热管理: 堆叠多个有源芯片会增加功率密度并可能导致热点。需要仔细进行热分析并可能使用热TSV。

2.供电: 为堆叠中的所有芯片提供稳定电源需要考虑TSV的电阻和电感。

3.测试: 需要新的测试策略来有效测试部分组装的3D堆叠并隔离缺陷。

4.信号完整性: TSV和微凸点引入了新的寄生效应,必须建模和管理。

5.机械应力: 材料之间热膨胀系数(CTE)的差异可能导致翘曲和可靠性问题。

6.成本: 3D集成工艺增加了成本,必须权衡性能和尺寸优势。

能够处理多芯片场景和TSV/微凸点模型的先进封装设计工具对成功开发3D IC非常必要。

应用和未来展望

3D集成技术在几个关键应用领域得到越来越多的采用:

1.高性能计算: HBM和先进的逻辑叠加逻辑堆叠,用于提高内存带宽和降低延迟。

2.移动设备: PoP和内存叠加逻辑堆叠,用于减小尺寸和提高性能。

3.成像: 具有单独感应和处理层的堆叠图像传感器。

4.异构集成: 结合不同工艺节点甚至不同半导体材料(如硅和III-V化合物)的芯片。

随着传统硅缩放变得更具挑战性和昂贵,3D集成预计将在继续实现类似摩尔定律的整体系统性能和功能缩放方面发挥越来越重要的作用。

正在进行的研究和开发的关键领域包括:

● 更细间距的TSV和微凸点

● 改进的热管理技术

● 增强的设计工具和方法

● 用于提高可靠性和性能的新材料

● 通过改进制造工艺降低成本

结论

3D IC集成和先进封装技术为在传统2D缩放之外继续提高电子系统性能、功能和尺寸提供了很有前途的途径。尽管仍然存在挑战,特别是在热管理和成本方面,但潜在的好处正在推动这些技术的快速发展。随着生态系统的成熟,可以期待看到3D集成在广泛应用领域的领先半导体产品中变得越来越普遍。

参考文献

[1] J. H. Lau, "Semiconductor Advanced Packaging," Singapore: Springer Nature Singapore Pte Ltd., 2021.

免责申明:本文内容转自:微信公众号“逍遥设计自动化”。文字、素材、图片版权等内容属于原作者,本站转载内容仅供大家分享学习。如果侵害了原著作人的合法权益,请及时与我们联系,我们会安排删除相关内容。本文内容为原作者观点,并不代表我们赞同其观点和(或)对其真实性负责。

先艺电子、XianYi、先艺、金锡焊片、Au80Sn20焊片、Solder Preform、芯片封装焊片供应商、芯片封装焊片生产厂家、芯片级三维系统集成技术、半导体互连和封装技术,芯片级散热技术、光伏焊带、银基钎料、助焊膏、高温助焊剂、高温焊锡膏、flux paste、陶瓷绝缘子封装、气密性封装、激光器巴条封装、热沉、IGBT大功率器件封装、光电子器件封装、预成型锡片、纳米银、纳米银膏、AMB载板、AuSn Alloy、TO-CAN封装、低温焊锡膏、喷印锡膏、银焊膏、银胶、烧结银、低温银胶、银烧结、silver sinter paste、Ceramic submount、预涂助焊剂焊片、气密封装焊料、气密性封焊、金锡热沉、金锡衬底、金锡焊料封装、芯片到玻璃基板贴片 (COG)、铟焊料封装、共晶焊、金锡烧结、金锡共晶烧结、共晶键合、金锡薄膜、金锡合金薄膜、合金焊料、金锡焊料、Au50Cu50焊片、Au焊片、Au88Ge12焊片、Au99Sb1焊片、Sn焊片、激光巴条金锡共晶焊、激光巴条焊接材料、背金锡、金锡盖板、金锡壳体、预置金锡壳体、预置金锡盖板、预涂焊料盖板、贴膜包装焊片、覆膜预成形焊片、金锡薄膜热沉、钨铜金锡热沉、SMT用预成形焊片、载带式预成形焊片、锡银焊料片、锡锑焊料片、中高温焊片、异形焊料片、IGBT焊料片、焊锡片、预成型锡片、金锡焊膏、纳米银锡膏、微组装焊料、金锡凸点、金锡bump、激光巴条共晶、Au80Sn20、AuSn Solder、晶振金锡封盖、电镀金锡、flux coating solder、共晶贴片、铟铅焊片、铟铅合金、锡铋焊片、锡铋焊料、金锡薄膜电路、ALN热沉、氮化铝热沉、碳化硅金锡热沉、SiC金锡热沉、金刚石热沉、硅基热沉、CMC热沉、CPC热沉

广州先艺电子科技有限公司是先进半导体连接材料制造商、电子封装解决方案提供商,我们可根据客户的要求定制专业配比的金、银、铜、锡、铟等焊料合金,加工成预成形焊片,提供微电子封装互连材料、微电子封装互连器件和第三代功率半导体封装材料系列产品,更多资讯请看www.xianyichina.com,或关注微信公众号“先艺电子”。